此次会议是自2020年以来初次全线多名研究人员参会,同享该范畴的最新技能。约有200项芯片实测效果当选,约45%的芯片效果来自于英特尔、三星、台积电、AMD、英伟达、高通、博通、ADI、TI、联发科等世界芯片巨子公司,其他芯片效果来自于高校和科研院所。

东南大学电子科学与工程学院/集成电路学院的师生赴美参加此次盛会,国家ASIC工程中心杨军教授、司鑫副研究员和蔡浩副教授课题组,在存储器范畴的Session7和Session33报告了三项存内核算芯片研究效果,是本届ISSCC在存储器-存内核算范畴报导数量最多的单位之一。一起,东南大学作为IEEE固态电路南京分会主席单位,派出代表参加本年度IEEE固态电路协会主席论坛。

面向高精度AI运算场景,针对整型神经网络在杂乱使命下功能一会儿就下降的问题,东南大学团队提出一套根据同享指数的浮点存算架构,经过片外权重指数域对指,片上指数相加对指,大局浮点部分定点的方法,完成浮点运算。一起规划了一套高位全精度、低位近似的数字运算架构,以别离字线方法完成了数字域的高能效运算。经过对数字域存算的加法树结构能够进行分化,权重、特征值、通道三段加法树的重组完成核算功率的进步。

面向Edge端神经网路的加快使命,传统的存内核算规划面对许多问题和应战,最重要的包括短累加致能效下降、阵列利用率低,数据更新本钱高和核算-读出拜访时刻过长等。东南大学团队提出一种用于Edge端神经网络加快的存内核算芯片规划。架构层面,初次提出一种灵敏可装备的存算一体阵列,支撑两种数据映射方法,在进步阵列利用率的一起可极大下降数据更新本钱。

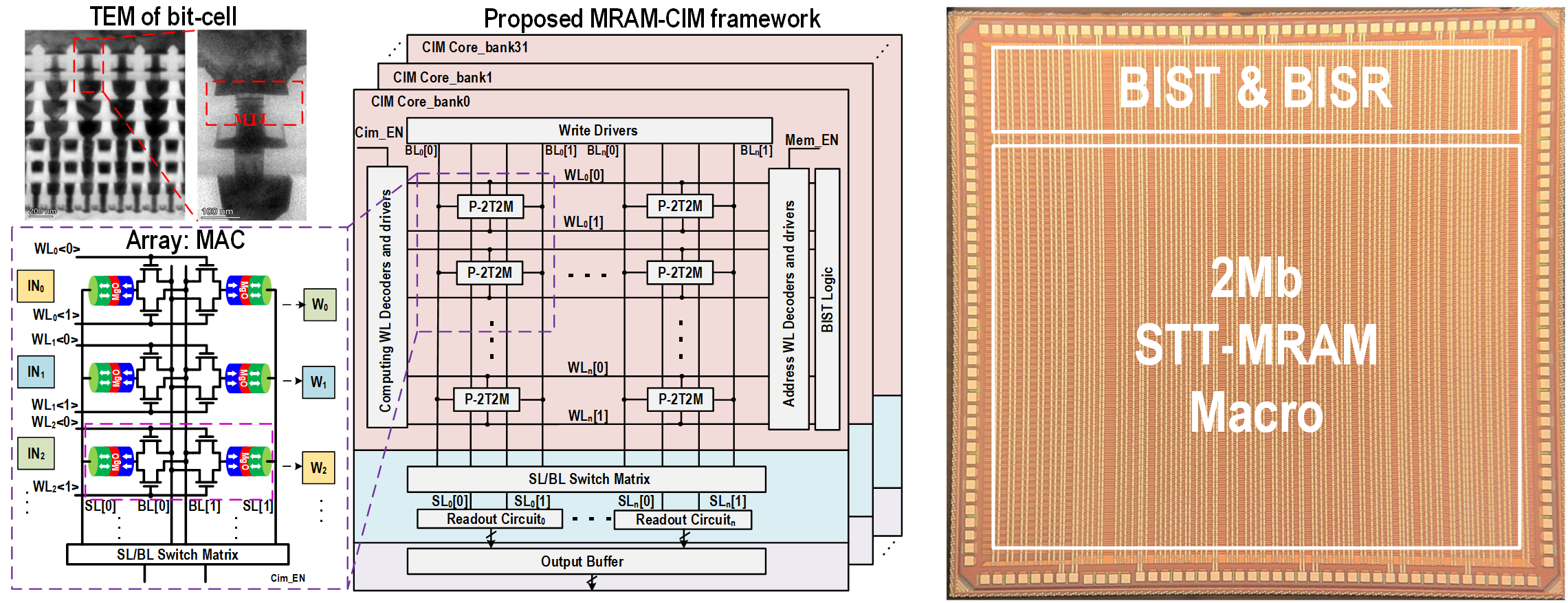

该作业面向资源受限的边际人工智能设备,处理了新式非易失磁存储器STT-MRAM存算电路自下而上规划中的应战。东南大学团队研发了一款28nm 2Mb的高能效STT-MRAM存内核算芯片,在1-bit输入/1-bit权重/9次累加/5-bit输出的情况下,完成了高达41.5 TOPS/W的峰值能效,以及96.2%(MNIST数据集)的网络推理精度,是中国大陆首篇在ISSCC上宣布的MRAM存储与存算作业。

据悉,ISSCC是由电气与电子工程协会(IEEE)固态电路学会资助建议的半导体集成电路规划范畴的学术会议,该会议于1954年初次举行,是该范畴尖端规划、最著名的世界会议。历史上当选ISSCC的效果代表着当年度全球领先水平,展现出芯片技能和工业的开展的新趋势,多项“芯片范畴里程碑式创造”在ISSCC初次发表,如世界上第一个集成模仿放大器芯片(1968年)、第一个8位微处理器芯片(1974年)和32位微处理器芯片(1981年)、第一个1Gb内存DRAM芯片(1995年)、第一个多核处理器芯片(2005年)等。